Nota:

El acceso a esta página requiere autorización. Puede intentar iniciar sesión o cambiar directorios.

El acceso a esta página requiere autorización. Puede intentar cambiar los directorios.

Controladores de miniporte que no admiten el procesamiento de recepción del controlador RSS, tal como se describe en este tema.

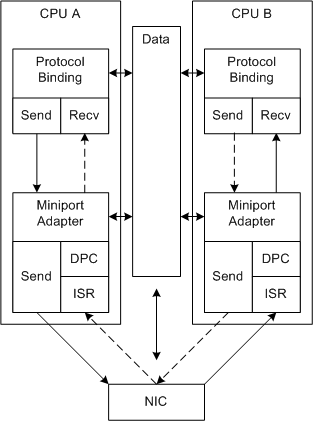

En la ilustración siguiente se muestra el procesamiento de recepción no RSS.

En la ilustración, las rutas de acceso discontinuas representan una ruta alternativa para el procesamiento de envío y recepción. Dado que el sistema controla el escalado, el procesamiento no siempre se produce en la CPU que proporciona el mejor rendimiento. Las conexiones se procesan en la misma CPU durante interrupciones sucesivas solo de manera aleatoria.

El siguiente proceso se repite para cada ciclo de interrupción no RSS:

La NIC usa DMA para rellenar un búfer con datos recibidos e interrumpe el sistema.

El controlador de miniporta asignó los búferes de recepción en memoria compartida durante la inicialización.

La NIC puede seguir rellenando búferes de recepción adicionales en cualquier momento en este ciclo de interrupción. Sin embargo, la NIC no interrumpe de nuevo hasta que el controlador de miniporte habilita interrupciones.

Los búferes recibidos que controla el sistema en un ciclo de interrupción se pueden asociar a muchas conexiones de red diferentes.

NDIS invoca la función MiniportInterrupt (ISR) del controlador de miniport en una CPU determinada por el sistema.

Idealmente, el ISR debe ir a la CPU menos ocupada. Sin embargo, en algunos sistemas, el sistema asigna el ISR a una CPU disponible o a una CPU asociada a la NIC.

El ISR deshabilita las interrupciones y solicita a NDIS poner en cola una llamada a procedimiento diferido (DPC) para procesar los datos recibidos.

NDIS llama a la función MiniportInterruptDPC (DPC) en la CPU actual.

Las compilaciones DPC reciben descriptores para todos los búferes recibidos e indican los datos de la pila de controladores. Para obtener más información, consulte Recepción de datos de red.

Puede haber muchos búferes para muchas conexiones diferentes y puede haber mucho procesamiento para completar. Los datos recibidos asociados a los ciclos de interrupción posteriores se pueden procesar en otras CPU. El procesamiento de envío de una conexión de red determinada también se puede ejecutar en una CPU diferente.

El DPC habilita las interrupciones. Este ciclo de interrupción se completa y el proceso se inicia de nuevo.