Observação

O acesso a essa página exige autorização. Você pode tentar entrar ou alterar diretórios.

O acesso a essa página exige autorização. Você pode tentar alterar os diretórios.

Os drivers de miniport que não dão suporte ao processamento de recebimento do RSS, conforme descrito neste tópico.

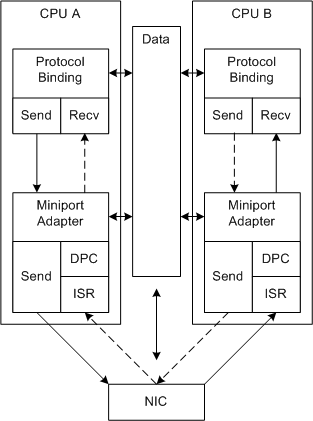

A figura a seguir ilustra o processamento de recebimento não RSS.

Na figura, os caminhos tracejados representam um caminho alternativo para o processamento de envio e recebimento. Como o sistema controla o dimensionamento, o processamento nem sempre ocorre na CPU que fornece o melhor desempenho. As conexões são processadas na mesma CPU por interrupções sucessivas apenas por acaso.

O processo a seguir se repete para cada ciclo de interrupção não RSS:

A NIC usa o DMA para preencher um buffer com dados recebidos e interrompe o sistema.

O driver de miniporto alocou os buffers de recebimento na memória compartilhada durante a inicialização.

A NIC pode continuar a preencher buffers de recebimento adicionais a qualquer momento neste ciclo de interrupção. No entanto, a NIC não interromperá novamente até que as interrupções sejam habilitadas pelo driver de miniporte.

Os buffers recebidos que o sistema manipula em um ciclo de interrupção podem ser associados a muitas conexões de rede diferentes.

O NDIS chama a ISR (função MiniportInterrupt ) do driver de miniporto em uma CPU determinada pelo sistema.

Idealmente, o ISR deve ir para a CPU menos ocupada. No entanto, em alguns sistemas, o sistema atribui o ISR a uma CPU disponível ou a uma CPU associada à NIC.

O ISR desativa as interrupções e solicita ao NDIS que enfileire uma chamada de procedimento adiado (DPC) para processar os dados recebidos.

O NDIS chama a função MiniportInterruptDPC (DPC) na CPU atual.

As compilações do DPC recebem descritores para todos os buffers recebidos e indicam os dados na pilha de drivers. Para obter mais informações, consulte Como receber dados de rede.

Pode haver muitos buffers para muitas conexões diferentes e há potencialmente muito processamento a ser concluído. Os dados recebidos associados aos ciclos de interrupção subsequentes podem ser processados em outras CPUs. O processamento de envio para uma determinada conexão de rede também pode ser executado em uma CPU diferente.

O DPC habilita as interrupções. Esse ciclo de interrupção é concluído e o processo é iniciado novamente.