Nota

O acesso a esta página requer autorização. Podes tentar iniciar sessão ou mudar de diretório.

O acesso a esta página requer autorização. Podes tentar mudar de diretório.

Em algumas plataformas, o processador e o controlador DMA do sistema (ou adaptadores DMA bus-master) apresentam anomalias de coerência de cache. As diretrizes a seguir permitem que os drivers que usam a versão 1 ou 2 da interface de operações DMA (consulte DMA_OPERATIONS) mantenham estados de cache coerentes em todas as arquiteturas de processador suportadas, incluindo arquiteturas que não contêm hardware para impor automaticamente a coerência do cache.

Nota As diretrizes neste tópico aplicam-se apenas aos drivers que usam as versões 1 e 2 da interface de operações DMA. Os drivers que usam a versão 3 dessa interface devem seguir um conjunto diferente de diretrizes. Para obter mais informações, consulte Versão 3 da Interface de Operações DMA.

Para manter a integridade dos dados durante as operações DMA, os drivers de nível mais baixo devem seguir estas diretrizes

Chame KeFlushIoBuffers antes de iniciar uma operação de transferência para manter a consistência entre os dados que podem ser armazenados em cache no processador e os dados na memória.

Se um driver chamar AllocateCommonBuffer com o parâmetro CacheEnabled definido como TRUE, o driver deverá chamar KeFlushIoBuffers antes de iniciar uma operação de transferência para/de o seu buffer.

Chame FlushAdapterBuffers no final de cada operação de transferência de dispositivo para ter certeza de que todos os bytes restantes nos buffers do controlador DMA do sistema foram gravados na memória ou no dispositivo subordinado.

Ou, chame FlushAdapterBuffers no final de cada operação de transferência para um determinado IRP para ter certeza de que todos os dados foram lidos na memória do sistema ou gravados em um dispositivo DMA bus-master.

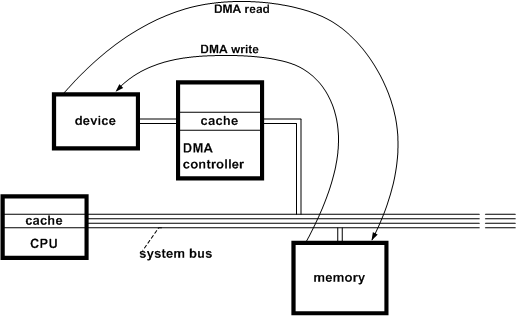

A figura a seguir mostra por que é importante liberar o cache do processador antes de uma operação de leitura ou gravação usando DMA se o processador host e o controlador DMA não mantiverem automaticamente a coerência do cache.

Uma operação assíncrona de leitura ou gravação DMA acessa dados na memória, não no cache do processador. A menos que esse cache tenha sido liberado chamando KeFlushIoBuffers pouco antes de uma leitura, os dados transferidos para a memória do sistema pela operação DMA podem ser substituídos por dados obsoletos se o cache do processador for liberado posteriormente. A menos que o cache do processador tenha sido liberado chamando KeFlushIoBuffers pouco antes de uma gravação, os dados nesse cache podem estar mais up-to-date do que a cópia na memória.

KeFlushIoBuffers não faz nada se puder contar com o processador e o controlador DMA para manter a coerência do cache, portanto, as chamadas para esta rotina de suporte praticamente não têm sobrecarga em tal plataforma.

Como também mostrado na figura anterior, os controladores DMA, que são representados por objetos do adaptador, podem ter buffers internos. Esse controlador DMA pode transferir dados armazenados em cache em blocos de tamanho fixo, geralmente oito ou mais bytes de cada vez. Além disso, esses controladores DMA podem esperar até que seus buffers internos estejam cheios antes de cada operação de transferência.

Considere o caso de um driver de nível mais baixo que usa DMA subordinado para ler dados em blocos de tamanho variável ou em blocos de tamanho fixo que não são um múltiplo integral do tamanho de cache de um controlador DMA do sistema. A menos que esse driver chame FlushAdapterBuffers no final de cada transferência de dispositivo, não é possível ter certeza de quando cada byte que o driver solicitado realmente será transferido.

O driver de um dispositivo DMA bus-master também deve chamar FlushAdapterBuffers no final de cada operação de transferência de um IRP, para garantir que todos os dados foram transferidos para a memória do sistema ou enviados para o dispositivo.

FlushAdapterBuffers retorna um valor booleano, que indica se a operação de liberação solicitada foi bem-sucedida. Um driver pode usar esse valor para determinar como definir o bloco de status de E/S ao concluir um IRP para uma operação de leitura ou gravação DMA.